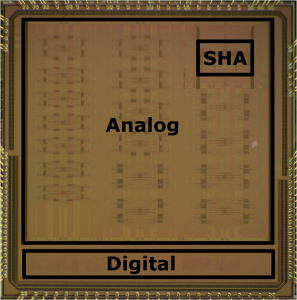

A 15-bit 125-MS/s two-channel time-interleaved pipelined ADC is fabricated in a 0.18 um CMOS technology, and achieves 91.9 dB SFDR, 69.9 dB SNDR for a 9.99 MHz input. This ADC incorporates a single sample-and-hold amplifier which employs a precharged circuit configuration to mitigate performance requirements for its opamp. Digital background calibration is applied to maintain the conversion linearity of each A/D channel and also correct both gain and offset mismatches between the two channels. Excluding I/O buffers, the chip occupies an area of 4.3×4.3 mm2 and dissipates 909 mW from a 1.8 V supply.

A 15-bit 125-MS/s two-channel time-interleaved pipelined ADC is fabricated in a 0.18 um CMOS technology, and achieves 91.9 dB SFDR, 69.9 dB SNDR for a 9.99 MHz input. This ADC incorporates a single sample-and-hold amplifier which employs a precharged circuit configuration to mitigate performance requirements for its opamp. Digital background calibration is applied to maintain the conversion linearity of each A/D channel and also correct both gain and offset mismatches between the two channels. Excluding I/O buffers, the chip occupies an area of 4.3×4.3 mm2 and dissipates 909 mW from a 1.8 V supply.

Publication: (1) Z-M Lee, C-Y Wang, and J-T Wu, “A CMOS 15-bit 125-MS/s Time-Interleaved ADC With Digital Background Calibration,” IEEE Journal of Solid-State Circuits, Vol. 42, No. 10, pp. 2149-2160, Oct. 2007. (2) Z-M Lee, C-Y Wang, and J-T Wu, “A CMOS 15-Bit 125-MS/s Time-Interleaved ADC with Digital Background Calibration,” 2006 IEEE Custom Integrated Circuits Conference, pp. 209-212, Sept. 2006.