A 250 MHz analog baseband chain for Ultra-Wideband was implemented in a 1.2 V0.13 um CMOS process. The chip has an active area of 0.8 mm square. In the analog baseband, PGAs and filters are carried out by current-mode amplifiers to achieve wide bandwidth and wide dynamic range of gain, as well as low noise and high linearity. Besides, a current-mode Sallen–Key low-pass filter … 閱讀全文… 關於 A 250 MHz 14 dB-NF 73 dB-Gain 82 dB-DR Analog Baseband Chain With Digital-Assisted DC-Offset Calibration for Ultra-Wideband

研究成果

A 1.2 V 114 mW Dual-Band Direct-Conversion DVB-H Tuner in 0.13-um CMOS

A fully integrated direct-conversion tuner is implemented in 0.13 um CMOS technology. A broadband noise-canceling balun LNA with the proposed dual cross-coupling technique helps achieve an overall receiver noise figure from 3.7 to 4.3 dB while consuming only 3.6 mW. The proposed current-mode switching scheme improves the achievable SNIR with a gain step of 15 dB, providing … 閱讀全文… 關於 A 1.2 V 114 mW Dual-Band Direct-Conversion DVB-H Tuner in 0.13-um CMOS

A 2.4–5.4-GHz Wide Tuning-Range CMOS Reconfigurable Low-Noise Amplifier

A 2.4–5.4-GHz CMOS reconfigurable low-noise amplifier (LNA) is designed. It consists of two stages: a broadband input stage for a steady input matching and noise performance, and a reconfigurable band-selective stage which provides a wide-range frequency tuning from 2.4 to 5.4 GHz and a 12-dB stepped gain with linearity adjustment. The frequency tuning is conducted by a … 閱讀全文… 關於 A 2.4–5.4-GHz Wide Tuning-Range CMOS Reconfigurable Low-Noise Amplifier

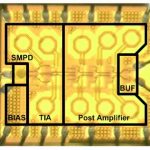

A 10-Gbps CMOS Single Chip Optical Receiver with 2-D Meshed Spatially-Modulated Light Detector

This chip describes the design of a 10-Gb/s fully integrated CMOS optical receiver, which consists of a novel spatially-modulated photo detector (SMPD), a low-noise trans-impedance amplifier (TIA), and a post limiting amplifier on a single chip. The bandwidth of proposed meshed SMPD can be boosted up to 6.9 GHz under a reverse-biased voltage of 14.2 V. The operating speed of … 閱讀全文… 關於 A 10-Gbps CMOS Single Chip Optical Receiver with 2-D Meshed Spatially-Modulated Light Detector

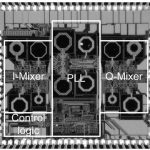

A 3-10 GHz, 14-Band CMOS Frequency Synthesizer with Spurs Reduction for MB-OFDM UWB System

A 3-10 GHz, 14 Band CMOS frequency synthesizer with spurs reduction for MB-OFDM UWB system is presented. Based on a single PLL and two-stage frequency mixing architecture, the image spurs are suppressed below -45dBc and improved by more than 22 dB incorporating with I/Q calibration for the single side band mixers. Implemented in a 0.18-μm CMOS technology, this chip drains 65 mA … 閱讀全文… 關於 A 3-10 GHz, 14-Band CMOS Frequency Synthesizer with Spurs Reduction for MB-OFDM UWB System