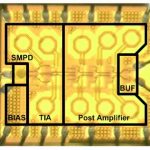

This chip describes the design of a 10-Gb/s fully integrated CMOS optical receiver, which consists of a novel spatially-modulated photo detector (SMPD), a low-noise trans-impedance amplifier (TIA), and a post limiting amplifier on a single chip. The bandwidth of proposed meshed SMPD can be boosted up to 6.9 GHz under a reverse-biased voltage of 14.2 V. The operating speed of … 閱讀全文… 關於 A 10-Gbps CMOS Single Chip Optical Receiver with 2-D Meshed Spatially-Modulated Light Detector

陳巍仁

A 3-10 GHz, 14-Band CMOS Frequency Synthesizer with Spurs Reduction for MB-OFDM UWB System

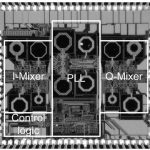

A 3-10 GHz, 14 Band CMOS frequency synthesizer with spurs reduction for MB-OFDM UWB system is presented. Based on a single PLL and two-stage frequency mixing architecture, the image spurs are suppressed below -45dBc and improved by more than 22 dB incorporating with I/Q calibration for the single side band mixers. Implemented in a 0.18-μm CMOS technology, this chip drains 65 mA … 閱讀全文… 關於 A 3-10 GHz, 14-Band CMOS Frequency Synthesizer with Spurs Reduction for MB-OFDM UWB System

A 7.1 mW, 10-GHz All Digital Frequency Synthesizer with Dynamically Reconfigured Digital Loop Filter in 90 nm CMOS Technology

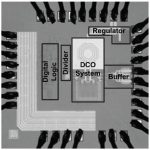

A 10 GHz all digital frequency synthesizer (ADPLL) with dynamic digital loop filter is presented. Governed by a proposed locking process monitor (LPM), the digital loop filter is automatically reconfigured during the frequency acquisition and phase tracking process. The loop bandwidth is also self-adjusted during the locking process so as to achieve fast lock and low noise … 閱讀全文… 關於 A 7.1 mW, 10-GHz All Digital Frequency Synthesizer with Dynamically Reconfigured Digital Loop Filter in 90 nm CMOS Technology