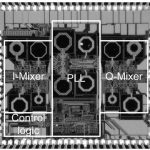

A 3-10 GHz, 14 Band CMOS frequency synthesizer with spurs reduction for MB-OFDM UWB system is presented. Based on a single PLL and two-stage frequency mixing architecture, the image spurs are suppressed below -45dBc and improved by more than 22 dB incorporating with I/Q calibration for the single side band mixers. Implemented in a 0.18-μm CMOS technology, this chip drains 65 mA … 閱讀全文… 關於 A 3-10 GHz, 14-Band CMOS Frequency Synthesizer with Spurs Reduction for MB-OFDM UWB System

研究成果

A 16-mW 8-Bit 1-GS/s Subranging ADC in 55nm CMOS

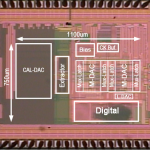

An 8-bit subranging ADC was fabricated using a 55nm CMOS technology. To enhance speed, subranging is executed by activating comparators in the digital domain. To save power, comparators are latches with automatic offset calibration. Operating at 1GHz sampling rate, the ADC consumes 16mW from a 1.2V supply. The measured DNL is 0.8LSB and INL is 1.2LSB. The measured SFDR and SNDR … 閱讀全文… 關於 A 16-mW 8-Bit 1-GS/s Subranging ADC in 55nm CMOS

A 12-Bit 1.25-GS/s DAC in 90 nm CMOS

A current-steering digital-to-analog converter (DAC) was fabricated using a 90 nm CMOS technology. Its dynamic performance is enhanced by adopting a digital random return-to-zero (DRRZ) operation and a compact current cell design. The DRRZ also facilitates a current-cell background calibration technique that ensures the DAC static linearity. The measured differential … 閱讀全文… 關於 A 12-Bit 1.25-GS/s DAC in 90 nm CMOS

A CMOS 8-Bit 1.6-GS/s DAC with Digital Random Return-to-Zero

A digital random-return-to-zero (DRRZ) technique is presented to improve the dynamic performance of current-steering digital-to-analog converters (DACs). To demonstrate the proposed technique, a CMOS 8-bit 1.6-GS/s DAC was fabricated in a 90 nm CMOS technology. The DAC achieves a spurious-free dynamic range (SFDR) better than 60 dB for a sinewave input up to 460 MHz, and better … 閱讀全文… 關於 A CMOS 8-Bit 1.6-GS/s DAC with Digital Random Return-to-Zero

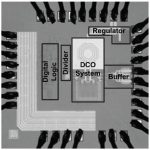

A 7.1 mW, 10-GHz All Digital Frequency Synthesizer with Dynamically Reconfigured Digital Loop Filter in 90 nm CMOS Technology

A 10 GHz all digital frequency synthesizer (ADPLL) with dynamic digital loop filter is presented. Governed by a proposed locking process monitor (LPM), the digital loop filter is automatically reconfigured during the frequency acquisition and phase tracking process. The loop bandwidth is also self-adjusted during the locking process so as to achieve fast lock and low noise … 閱讀全文… 關於 A 7.1 mW, 10-GHz All Digital Frequency Synthesizer with Dynamically Reconfigured Digital Loop Filter in 90 nm CMOS Technology