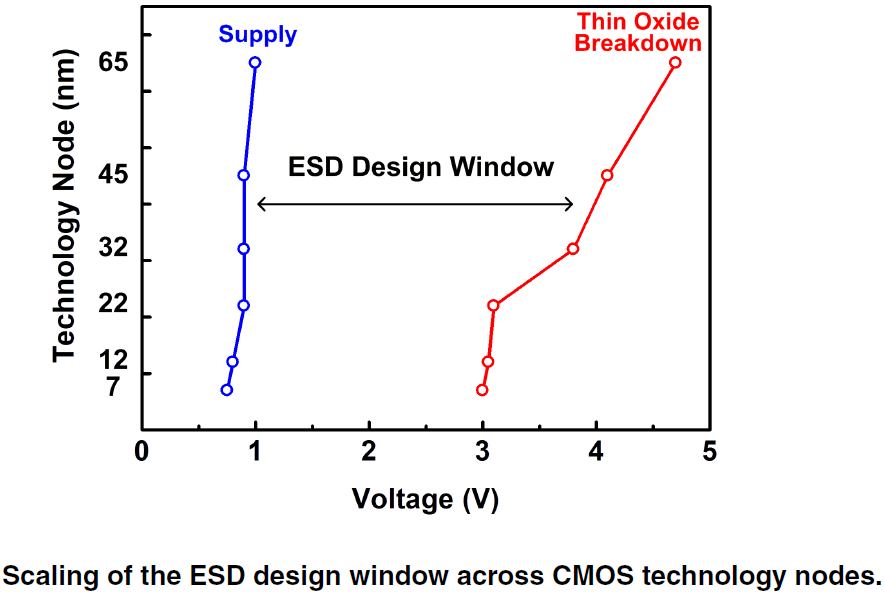

Electrostatic discharge (ESD) remains a critical reliability issue in CMOS technologies. This article reviews the fundamentals of ESD phenomena and introduces representative on-chip protection structures. To address the shrinking margin between supply voltage and gate oxide breakdown, the concept of the ESD design window is introduced as a fundamental constraint for selecting and sizing protection devices. The inherent tradeoff between ESD robustness and latch-up immunity is also addressed, highlighting strategies to prevent accidental activation during normal operation. It is further indicated that effective ESD protection is a comprehensive chip-level requirement that extends beyond I/O pads to include robust power-rail clamping and internal protection. Diode-based protection, silicon-controlled rectifier (SCR)-based devices, and MOS clamps are discussed with emphasis on their operating principles, discharge paths, and design tradeoffs. The coordination between I/O protection and power-rail clamps is highlighted as an essential requirement for forming complete discharge paths during ESD events. In addition to presenting the key device and circuit concepts, this article also clarifies how these structures are typically integrated into practical chip designs, providing readers with both intuitive understanding and circuit-level design guidelines that can be directly applied in design practice. Finally, future challenges are outlined, including the impact of advanced technology scaling, 3-D integration, chiplet-based architectures, and increasingly stringent system-level standards. By combining fundamental insights with circuit-level perspectives, this article aims to serve as a clear and accessible tutorial foundation, helping circuit designers and researchers build a comprehensive understanding of ESD protection for modern and future semiconductor technologies, and supporting continued progress in reliable electronic system design.

Chun-Yu Lin and Ming-Dou Ker, “ESD protection design: fundamentals and advanced strategies,” IEEE Open J. Solid-State Circuits Society, vol. 6, pp. 61-76, Mar. 2026, doi: 10.1109/OJSSCS.2026.3667840