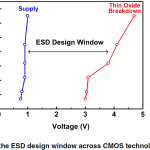

Electrostatic discharge (ESD) remains a critical reliability issue in CMOS technologies. This article reviews the fundamentals of ESD phenomena and introduces representative on-chip protection structures. To address the shrinking margin between supply voltage and gate oxide breakdown, the concept of the ESD design window is introduced as a fundamental constraint for selecting … 閱讀全文… 關於 ESD Protection Design: Fundamentals and Advanced Strategies

研究成果

Review of Low-C ESD Protection Designs forHigh-Speed and High-Frequency Applications

The increasing complexity and integration of high-speed and high-frequency electronic systems have heightened the need for robust on-chip electrostatic discharge (ESD) protection to meet stringent reliability requirements. However, integrating ESD protection into these systems is challenging, as conventional protection devices introduce parasitic capacitance that degrades … 閱讀全文… 關於 Review of Low-C ESD Protection Designs forHigh-Speed and High-Frequency Applications

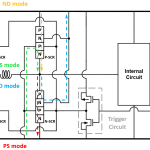

Power-Clamp-Triggered SCR for Broadband RF ESD Protection

A compact electrostatic discharge (ESD) protection circuit using silicon-controlled rectifiers (SCRs) for radio frequency (RF) I /O interfaces is proposed and implemented in the TSMC 0.18- μ m CMOS process. The design ensures robust ESD protection by enabling discharge through multiple paths between the I /O pins and power rails. To mitigate the parasitic capacitance introduced … 閱讀全文… 關於 Power-Clamp-Triggered SCR for Broadband RF ESD Protection

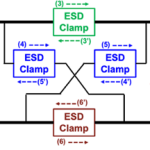

Compact ESD Protection Device for Separated Power Domain Application

Advanced CMOS chips are often integrated with multiple power domains to fulfill sophisticated functionalities, which complicates cross-power domain electrostatic discharge (ESD) protection. In this work, a novel silicon-controlled rectifier (SCR) device, named nMOS-triggered dual-power SCR (NMT_DP_SCR), featuring up to 12 discharge paths for ESD protection, is proposed and … 閱讀全文… 關於 Compact ESD Protection Device for Separated Power Domain Application

All-NMOS Power-Rail ESD Clamp Circuit with Compact Area and Low Leakage

Integrated circuits (ICs) are susceptible to breakage due to electrostatic discharge (ESD), making ESD protection circuits necessary for ICs. In some applications, internal circuits may adopt an all N-type transistor design. In such cases, the ESD protection circuit should only use N-type transistors to reduce the number of process masks required. This work proposes both a … 閱讀全文… 關於 All-NMOS Power-Rail ESD Clamp Circuit with Compact Area and Low Leakage