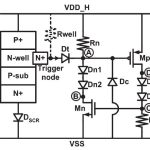

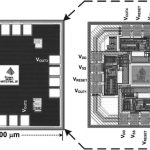

Diode-triggeredsilicon-controlled rectifiers(DTSCRs) are used for on-chip electrostatic discharge protection. The role of the trigger diode string in determining the transient voltage overshoot is investigated using a very fast transmission line pulse. A DTSCR containing only poly-bound trigger diodes has a voltage overshoot of just 1.5 V at 7 A, which is significantly less … 閱讀全文… 關於 Diode-triggered silicon-controlled rectifier with reduced voltage overshoot for CDM ESD protection

研究成果

ESD protection design for 60-GHz LNA with inductor-triggered SCR in 65-nm CMOS process

To effectively protect the radio-frequency (RF) circuits in nanoscale CMOS technology from electrostatic discharge (ESD) damages, the silicon-controlled rectifier (SCR) devices have been used as main on-chip ESD protection devices due to their high ESD robustness and low parasitic capacitance. In this paper, an SCR device assisted with an inductor is proposed to improve the … 閱讀全文… 關於 ESD protection design for 60-GHz LNA with inductor-triggered SCR in 65-nm CMOS process

New design of 2 × VDD-tolerant power-rail ESD clamp circuit for mixed-voltage IO buffers in 65-nm CMOS technology

A new 2 × VDD-tolerant power-rail electrostatic discharge (ESD) clamp circuit realized with only thin gate oxide 1-V (1 × VDD) devices and a silicon-controlled rectifier (SCR) as the main ESD clamp device has been proposed and verified in a 65-nm CMOS process. This new design has a low standby leakage current by reducing the voltage difference across the gate oxide of the … 閱讀全文… 關於 New design of 2 × VDD-tolerant power-rail ESD clamp circuit for mixed-voltage IO buffers in 65-nm CMOS technology

New 4-bit transient-to-digital converter for system-level ESD protection in display panels

A new on-chip 4-bit transient-to-digital converter for system-level electrostatic discharge (ESD) protection design is proposed. The proposed converter is designed to detect ESD-induced transient disturbances and transfer different ESD voltages into digital codes under system-level ESD tests. The experimental results in a 0.13-μm CMOS integrated circuit with 1.8-V devices have … 閱讀全文… 關於 New 4-bit transient-to-digital converter for system-level ESD protection in display panels

Stimulus driver for epilepsy seizure suppression with adaptive loading impedance

A stimulus driver circuit for micro-stimulator used in implantable device was presented in this paper. For epileptic seizure control, the target of the driver was to output 30-μA stimulus currents when the electrode impedance varied within 20 and 200 kΩ. The driver, which consisted of output stage, control block, and adaptor, has been integrated in a single chip. The averaged … 閱讀全文… 關於 Stimulus driver for epilepsy seizure suppression with adaptive loading impedance