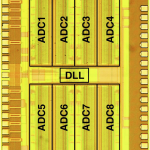

An 8-channel 6-bit 16-GS/s time-interleaved ADC was fabricated using a 65nm CMOS technology. Each A/D channel is a flash ADC using latch-type comparator with background offset calibration. Timing skews among the channels are also continuously calibrated in the background. The chip achieves 42.3dB SFDR and 30.8dB SNDR at 16 GS/s sampling rate. Publications: (1) C-C Huang and … 閱讀全文… 關於 A CMOS 6-Bit 16-GS/s Time-Interleaved ADC

研究成果

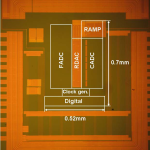

A CMOS 6-mW 10-bit 100-MS/s Two-Step ADC

A 10-bit 100-MS/s two-step ADC was fabricated using a 90 nm CMOS technology. To reduce power consumption, the ADC uses latch-type comparators for signal digitalization and an open-loop amplifier for residue amplification. The accuracy of the comparators is improved by offset calibration. The gain accuracy and the linearity of the residue amplifier are enhanced by digital … 閱讀全文… 關於 A CMOS 6-mW 10-bit 100-MS/s Two-Step ADC

互補式金氧半積體電路之靜電放電防護

靜電放電(Electrostatic Discharge, ESD)是造成大多數的電子元件或電子系統受到過度電性應力(Electrical Overstress, EOS)破壞的主要因素。這種破壞會導致半導體元件以及電腦系統等,形成一種永久性的毀壞,因而影響 積體電路(Integrated Circuits, … 閱讀全文… 關於 互補式金氧半積體電路之靜電放電防護

A CMOS 15-Bit 125-MS/s Time-Interleaved ADC

A 15-bit 125-MS/s two-channel time-interleaved pipelined ADC is fabricated in a 0.18 um CMOS technology, and achieves 91.9 dB SFDR, 69.9 dB SNDR for a 9.99 MHz input. This ADC incorporates a single sample-and-hold amplifier which employs a precharged circuit configuration to mitigate performance requirements for its opamp. Digital background calibration is applied to maintain … 閱讀全文… 關於 A CMOS 15-Bit 125-MS/s Time-Interleaved ADC