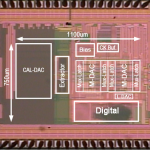

A current-steering digital-to-analog converter (DAC) was fabricated using a 90 nm CMOS technology. Its dynamic performance is enhanced by adopting a digital random return-to-zero (DRRZ) operation and a compact current cell design. The DRRZ also facilitates a current-cell background calibration technique that ensures the DAC static linearity. The measured differential … 閱讀全文… 關於 A 12-Bit 1.25-GS/s DAC in 90 nm CMOS

吳介琮

A CMOS 8-Bit 1.6-GS/s DAC with Digital Random Return-to-Zero

A digital random-return-to-zero (DRRZ) technique is presented to improve the dynamic performance of current-steering digital-to-analog converters (DACs). To demonstrate the proposed technique, a CMOS 8-bit 1.6-GS/s DAC was fabricated in a 90 nm CMOS technology. The DAC achieves a spurious-free dynamic range (SFDR) better than 60 dB for a sinewave input up to 460 MHz, and better … 閱讀全文… 關於 A CMOS 8-Bit 1.6-GS/s DAC with Digital Random Return-to-Zero

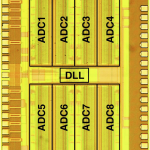

A CMOS 6-Bit 16-GS/s Time-Interleaved ADC

An 8-channel 6-bit 16-GS/s time-interleaved ADC was fabricated using a 65nm CMOS technology. Each A/D channel is a flash ADC using latch-type comparator with background offset calibration. Timing skews among the channels are also continuously calibrated in the background. The chip achieves 42.3dB SFDR and 30.8dB SNDR at 16 GS/s sampling rate. Publications: (1) C-C Huang and … 閱讀全文… 關於 A CMOS 6-Bit 16-GS/s Time-Interleaved ADC

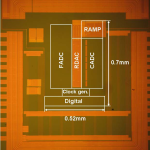

A CMOS 6-mW 10-bit 100-MS/s Two-Step ADC

A 10-bit 100-MS/s two-step ADC was fabricated using a 90 nm CMOS technology. To reduce power consumption, the ADC uses latch-type comparators for signal digitalization and an open-loop amplifier for residue amplification. The accuracy of the comparators is improved by offset calibration. The gain accuracy and the linearity of the residue amplifier are enhanced by digital … 閱讀全文… 關於 A CMOS 6-mW 10-bit 100-MS/s Two-Step ADC

A CMOS 15-Bit 125-MS/s Time-Interleaved ADC

A 15-bit 125-MS/s two-channel time-interleaved pipelined ADC is fabricated in a 0.18 um CMOS technology, and achieves 91.9 dB SFDR, 69.9 dB SNDR for a 9.99 MHz input. This ADC incorporates a single sample-and-hold amplifier which employs a precharged circuit configuration to mitigate performance requirements for its opamp. Digital background calibration is applied to maintain … 閱讀全文… 關於 A CMOS 15-Bit 125-MS/s Time-Interleaved ADC